# ADSP324-145

マルチファンクションボード

ハードウェア・ユーザーズ・マニュアル

中部電機株式会社

# 目 次

| 1. | 慨              | 記                                       | 1  |

|----|----------------|-----------------------------------------|----|

| 2. | 基Z             | ▶仕様                                     | 2  |

| 2  | . 1 .          | 機 能                                     | 2  |

| 2  | .2.            | ラインナップ                                  |    |

| 3. | 八-             | - ドウェア                                  | 6  |

| 3  | .1.            | コネクタ、ディップスイッチの配置                        | 6  |

| _  | . 2 .          | 出荷時の設定                                  |    |

|    | .3.            | ボードの設置方法                                |    |

| 4. |                | <b></b>                                 |    |

|    |                | 共 通                                     |    |

|    | .1.            | 共 週 · · · · · · · · · · · · · · · · · · |    |

|    | .3.            | P W M                                   |    |

| -  | . 4 .          | キャプチャ                                   |    |

|    | .5.            | パルスジェネレータカウンタ                           |    |

| 5  | 初甘             | 明設定                                     |    |

|    | بررا<br>. 1 .  | 共 通                                     |    |

|    | . 1 .          | パラレル入出力                                 |    |

| _  | .3.            | P W M                                   |    |

| _  | . 4 .<br>. 5 . | キャプチャ<br>パルスジェネレータ                      |    |

|    | . 6 .          | カウンタ                                    |    |

| 6. | ボ-             | -<br>- ドの制御とメモリマップ                      | 45 |

|    | . 1 .          | メモリマップ(アウトライン)                          |    |

|    | . 2 .          | 共 通                                     |    |

| _  | .3.            | パラレル入出力                                 |    |

| _  | . 4 .<br>. 5 . | PWM                                     |    |

|    | .6.            | パルスジェネレータ                               |    |

| 6  | .7.            | カウンタ                                    | 78 |

| 7. | 電              | 源                                       | 84 |

| 7  | .1.            | パラレル入出力機能を使用する場合                        |    |

|    | . 2 .          | P W M 機能を使用する場合                         |    |

|    | .3.            | キャプチャ機能を使用する場合<br>パルスジェネレータ機能を使用する場合    |    |

|    | . 5 .          | カウンタ機能を使用する場合                           |    |

| 8. | コネ             | ・<br>トクタのピン配列とピン配置                      | 86 |

| 8  | . 1 .          | ピン配列                                    | 86 |

|    | . 2 .          | ピン配置                                    |    |

| 9.         |              |      |

|------------|--------------|------|

| ()         | 行り           | ()/~ |

| 9          | [ ` <u> </u> | Mr)  |

| <i>-</i> . | ∤            |      |

# 図目次

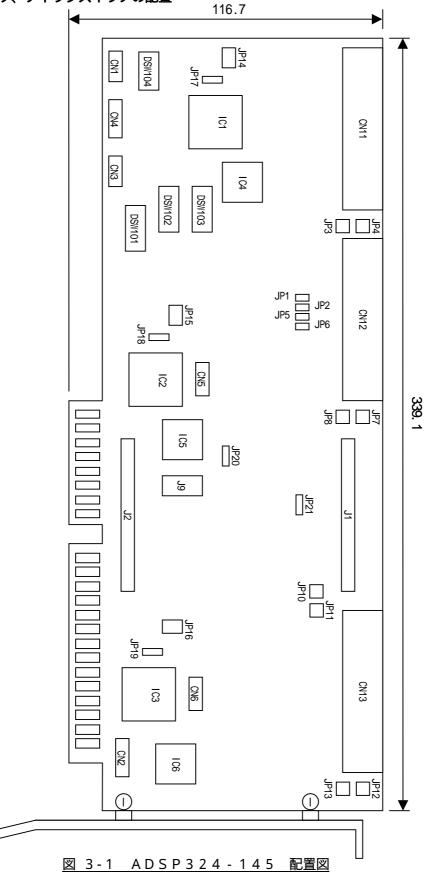

| 义 | 3-1 ADSP324-145 配置図                   | . 6 |

|---|---------------------------------------|-----|

| 义 | 3 - 2 ディップスイッチの出荷時設定                  | . 7 |

| 义 | 3 - 3 ジャンパースイッチの出荷時設定(1)              | . 8 |

| 义 | 3 - 4 ジャンパースイッチの出荷時設定(2)              | . 8 |

| 义 | 3 - 5 ジャンパースイッチの出荷時設定(3)              | . 9 |

| 义 | 3 - 6 ジャンパースイッチの出荷時設定(4)              | . 9 |

| 义 | 3 - 7 ジャンパースイッチの出荷時設定(5)              | 10  |

| 义 | 3 - 8 ジャンパースイッチの出荷時設定(6)              | 10  |

| 図 | 3 - 9 ジャンパースイッチの出荷時設定(7)              | 11  |

| 义 | 3 - 1 0 ジャンパースイッチの出荷時設定(8)            | 11  |

| 义 | , , , , , , , , , , , , , , , , , , , |     |

| _ | ,                                     | 12  |

| 义 | 3 - 1 3 ジャンパースイッチの出荷時設定(11)           | 12  |

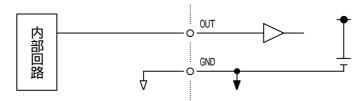

| 义 | 3-14 LVTTL出力回路                        | 14  |

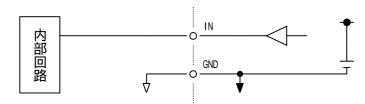

|   | 3-15 LVTTL入力回路                        |     |

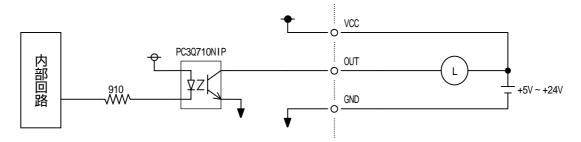

|   | 3 - 1 6 フォトカプラ絶縁出力回路                  |     |

|   |                                       |     |

|   | 3 - 1 8 PWM出力回路                       |     |

|   | 3 - 1 9 キャプチャ入力回路                     |     |

|   | 3 - 2 0 パルスジェネレータ出力回路                 |     |

|   | 3 - 2 1 カウンタ入力回路                      |     |

|   | 4-1 出力ポート下位 1 6 b i t                 |     |

|   | 4-2 出力ポート上位 1 6 b i t                 |     |

|   | 4-3 入力ポート下位 1 6 b i t                 |     |

|   | 4-4 入力ポート上位 1 6 b i t                 |     |

|   | 4-5 3相PWM出力の回路構成                      |     |

|   | 4 - 6 単相 P W M 出力の回路構成                |     |

|   | 4 - 7 PWM出力波形 フルブリッジの正出力              |     |

|   | 4 - 8 PWM出力波形 フルブリッジの逆出力              |     |

|   | 4 - 9 PWM出力波形 ハーフブリッジの正出力             |     |

|   | 4 - 1 0 PWM出力波形 ハーフブリッジの逆出力           |     |

|   | 4 - 1 1 同期パルス出力波形                     |     |

|   | 4 - 1 2 3相 P W M のキャプチャ可能回路構成         |     |

|   | 4 - 1 3 単相 P W M のキャプチャ可能回路構成         |     |

|   | 4-14 キャプチャした P W M 波形                 |     |

|   | 4 - 1 5 CW・CCWパルスの生成                  |     |

|   | 4 - 1 6 パルスジェネレータの出力波形                |     |

|   | 4 - 1 7 A B 相入力とカウントの関係               |     |

|   | 4 - 1 8 カウンタの逓倍                       | -   |

|   | 4 - 1 9 A B Z 相のカウンタリセット条件            |     |

|   | 5 - 1 ディップスイッチの論理表                    |     |

| _ | 5 - 2 ボードアドレスの設定                      |     |

| 巡 | 5 - 3 割り込みフラグの設定                      | 35  |

| _<br>図<br>図 | 6 - 1<br>6 - 2<br>8 - 1<br>8 - 2 | D u t y ・レジスタ         同期パルス出力・レジスタ         C N 4 を挿入方向から見たピン配置         C N 1 2 ・ C N 1 3 を挿入方向から見たピン配置 | 64<br>95 |

|-------------|----------------------------------|--------------------------------------------------------------------------------------------------------|----------|

|             | 0 2                              |                                                                                                        | 55       |

|             |                                  |                                                                                                        |          |

|             |                                  |                                                                                                        |          |

|             |                                  | 表目次                                                                                                    |          |

| 夷           | 1 - 1                            | マルチファンクションボードの一覧                                                                                       | 1        |

|             | 2 - 1                            | ラインナップの一覧                                                                                              |          |

|             | 3 - 1                            | DSPボードの接続コネクタ                                                                                          |          |

| 表           | 3 - 2                            | 拡張バスケーブル                                                                                               |          |

| 表           | 3 - 3                            | 機能別の接続コネクタ                                                                                             | 13       |

| 表           | 4 - 1                            | カウンタリセット条件                                                                                             | 32       |

| 表           | 5 - 1                            | DSW101~DSW103の信号割り付け表                                                                                  |          |

|             | 5 - 2                            | DSW104の信号割り付け表                                                                                         |          |

|             | 5 - 3                            | 割り込みコントロール・レジスタ                                                                                        |          |

|             | 5 - 4                            | モード選択・レジスタ                                                                                             |          |

|             | 5 - 5                            | ハンドリング方式・レジスタ                                                                                          |          |

|             | 5 - 6                            | ハンドリング信号の極性・レジスタ                                                                                       |          |

|             | 5 - 7<br>5 - 8                   | モード選択、出力許可・レジスタ<br>設定データ反映タイミング・レジスタ                                                                   |          |

|             | 5-8                              | 起たデータ反映タイミング・レジスタ<br>モード選択・レジスタ                                                                        |          |

|             | 5 - 1 (                          |                                                                                                        |          |

|             | 5 - 1                            |                                                                                                        |          |

|             | 6 - 1                            | ・                                                                                                      |          |

|             | 6 - 2                            | 機能「IOIO - 」の参照メモリマップ                                                                                   |          |

| 表           | 6 - 3                            | 機能「PWCN」の参照メモリマップ                                                                                      |          |

| 表           | 6 - 4                            | 機能「CPPL」の参照メモリマップ                                                                                      | 46       |

| 表           | 6 - 5                            | 機能「PWIO‐ 」の参照メモリマップ                                                                                    | 46       |

| 表           | 6 - 6                            | 機能「IOCN‐ 」の参照メモリマップ                                                                                    |          |

|             | 6 - 7                            | 共通領域のメモリマップ                                                                                            |          |

|             | 6 - 8                            | 割り込みコントロール・レジスタ                                                                                        |          |

|             | 6 - 9                            | 割り込みポートフラグ・レジスタ                                                                                        |          |

|             | 6-10                             |                                                                                                        | -        |

|             | 6 - 1 <sup>2</sup>               |                                                                                                        |          |

|             | 6-13                             |                                                                                                        |          |

|             | 6-14                             |                                                                                                        |          |

|             | 6 - 1 !                          |                                                                                                        |          |

|             | 6 - 1 (                          |                                                                                                        |          |

|             | 6 - 1                            |                                                                                                        |          |

| 表           | 6 - 18                           |                                                                                                        |          |

| 表           | 6 - 1 9                          | 9 モード選択、出力許可・レジスタ                                                                                      | 65       |

| 表           | 6 - 2 (                          |                                                                                                        |          |

| 表           | 6 - 2                            |                                                                                                        |          |

|             | 6 - 2 2                          |                                                                                                        |          |

|             | 6 - 2 3                          | ,                                                                                                      |          |

| 表           | 6 - 2 4                          | 4 計測完了フラグ・レジスタ                                                                                         | 72       |

| 表 | 6 - 2 | 5 モード選択・レジスタ                    | 72 |

|---|-------|---------------------------------|----|

| 表 | 6 - 2 | 6 パルスジェネレータ / パラレル入力のメモリマップ(1)  | 73 |

| 表 | 6 - 2 | 7 パルスジェネレータ / パラレル入力のメモリマップ(2)  | 74 |

| 表 | 6 - 2 | 8 パルスジェネレータ / パラレル入力のメモリマップ(3)  | 75 |

| 表 | 6 - 2 | 9 回転方向・レジスタ                     | 76 |

| 表 | 6 - 3 |                                 |    |

| 表 | 6 - 3 | 1 設定データ反映タイミング・レジスタ             | 77 |

| 表 | 6 - 3 | 2 パラレル出力 / カウンタのメモリマップ(1)       | 78 |

| 表 | 6 - 3 | 3 パラレル出力 / カウンタのメモリマップ(2)       | 79 |

| 表 | 6 - 3 | 4 パラレル出力 / カウンタのメモリマップ(3)       | 80 |

| 表 | 6 - 3 | 5 カウンタリセット許可・レジスタ               | 81 |

| 表 | 6 - 3 |                                 |    |

| 表 | 6 - 3 |                                 |    |

| 表 | 6 - 3 |                                 |    |

| 表 | 7 - 1 | パラレル入出力(LVTTL入出力)の電源ピン          | 84 |

| 表 | 7 - 2 | パラレル入出力(フォトカプラ絶縁入出力)の電源ピン       |    |

| 表 | 7 - 3 | P W M の電源ピン                     | 85 |

| 表 | 7 - 4 | キャプチャの電源ピン                      |    |

| 表 | 7 - 5 | パルスジェネレータの電源ピン                  | 85 |

| 表 | 7 - 6 | カウンタ ( カウンタ入力 ) の電源ピン           | 85 |

| 表 | 7 - 7 | カウンタ(フォトカプラ絶縁入力)の電源ピン           | 85 |

| 表 | 8 - 1 | 外部TTL入出力ポートのピン配列                | 86 |

| 表 | 8 - 2 | 外部入出力ポート0・1(パラレル入出力・LVTTL)のピン配列 | 87 |

| 表 | 8 - 3 | 外部入出力ポート0・1(パラレル入出力・絶縁)のピン配列    |    |

| 表 | 8 - 4 | 外部入出力ポート 0 ・ 1 ( PWM ) のピン配列    | 89 |

| 表 | 8 - 5 | 外部入出力ポート 0 ・ 1 (キャプチャ)のピン配列     | 90 |

| 表 | 8 - 6 | 外部入出力ポート2・3(パラレル入出力・LVTTL)のピン配列 | 91 |

| 表 | 8 - 7 | 外部入出力ポート2・3(パラレル入出力・絶縁)のピン配列    | 92 |

| 表 | 8 - 8 | 外部入出力ポート 2 ・ 3 (パルスジェネレータ)のピン配列 | 93 |

| 表 | 8 - 9 | 外部入出力ポート 2 ・ 3 (カウンタ)のピン配列      | 94 |

### 1.概 説

ADSP324-145は、32bitDSPボードADSP324、ADSP674-00シリーズ専用のマルチファンクションボードです。DSPの特徴である高速演算・高速I/Oを生かし、かつ、大規模ゲート数のFPGAを使用していますのでフレキシブルなI/Oを構築できます。

本ボードを用いることにより、パソコン又はタッチパネルによるGUI、DSPによるソフトウェア、FPGAによるハードウェアのトータルコーディネートが可能で、全体的にバランスの取れたシステム構築が可能です。

本ボードはパラレル入出力(LVTTL又はフォトカプラ絶縁)、PWM、キャプチャ、パルスジェネレータ、カウンタの5つの機能から2つを実装でき、DSPボードより直接制御することができます。(組み合わせによっては実装できない機能があります。)

また1台DSPボードに最大4台まで拡張可能です。

| マルチファンクションボード         | DSPボード                |

|-----------------------|-----------------------|

| A D S P 3 2 4 - 1 4 5 | A D S P 3 2 4 - 0 0 A |

| ADSP324-145           | ADSP674-00シリーズ        |

表 1-1 マルチファンクションボードの一覧

## 2.基本仕様

## 2.1. 機能

| 2.1.1. | パラレル入出力                               |                                         |

|--------|---------------------------------------|-----------------------------------------|

| 1)     | パラレル出力                                | 32bit出力 + 入出力制御信号 × 1ポート                |

|        |                                       | 16 bit単位での制御可能 ソフトウェアにより選択可             |

| 2)     | パラレル入力                                | 3 2 b i t 入力 + 入出力制御信号 × 1ポート           |

| ,      |                                       | 16 b i t 単位での制御可能 ソフトウェアにより選択可          |

| 3 )    | 入出力制御信号                               | ポート毎にSTB信号2点、ACK信号2点                    |

| 3 )    |                                       | 16 b i t 単位での制御可能 ソフトウェアにより選択可          |

| 4.5    | <b>)</b> 111 + 41/40 <del>2 - 1</del> |                                         |

| 4)     | 入出力制御方式                               | 制御なし、STB/ACK、ライトストローブ、ホールド              |

|        |                                       | (詳細は「4.2.2 ハンドリング方式」参照)                 |

|        |                                       | ソフトウェアにより選択可                            |

| 5)     | 割り込み信号                                | 入力ポートにて入出力制御を行った場合、割り込み可能               |

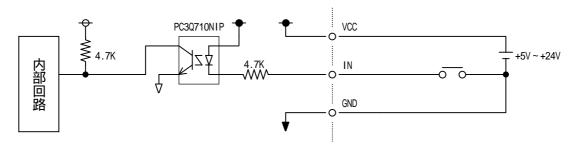

| 6)     | 入出力信号形式                               | LVTTL又はフォトカプラ絶縁(実装時に決定)                 |

| ,      | LVTTL                                 |                                         |

|        |                                       | + 5 V ~ + 2 4 V、定格電流 5 m A (PC3Q710NIP) |

|        | ノカーハノノmuna                            | · 5 · · · 2 · · · · · · · · · · · · · · |

|        |                                       |                                         |

| 2 4 2  | DWW (HIT)                             |                                         |

|        | PWM (出力)                              |                                         |

| 1)     | チャンネル数                                | 3相×3チャンネル又は単相×4チャンネル                    |

|        |                                       | (単相はHブリッジ回路の出力) ソフトウェアにより選択可            |

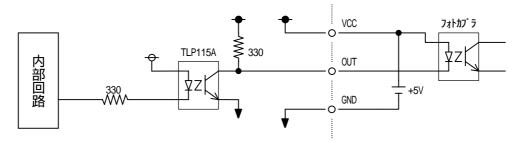

| 2)     | 出力仕様                                  | 高速フォトカプラ絶縁出力 + 5 V (TLP115A)            |

| •      |                                       | 負論理出力                                   |

|        |                                       | 只⊪注山/」                                  |

4) デューティー比 0~100%(分解能 キャリア周波数に依存)

なし

## 2.1.3. キャプチャ(入力)

5) デットタイム

7) 割り込み信号

6) 同期パルス出力

| 1) | チャンネル数  | PWM 3相×3チャンネル又はPWM単相×4チャンネル                       |

|----|---------|---------------------------------------------------|

|    |         | (単相はHブリッジ回路の入力) ソフトウェアにより選択可                      |

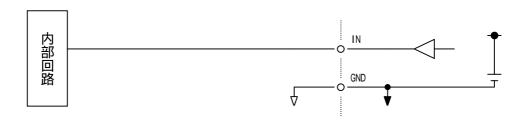

| 2) | 入力仕様    | LVTTL + 3.3V(+5V TTLとの接続可能)                       |

|    |         | 負論理入力                                             |

| 3) | 入力周波数   | 24Hz~120KHz(分解能 <sup>1</sup> / <sub>24MHz</sub> ) |

| 4) | デューティー比 | 0~100%(分解能 キャリア周波数に依存)                            |

|    |         | (入力周波数120KHzのとき1%計測可能)                            |

| 5) | 割り込み信号  | 計測完了にて割り込み可能                                      |

|    |         |                                                   |

(キャリア周波数120KHzのとき1%制御可能)

PWM周期に同期したパルス出力(1~255で分周可能) LVTTL +3.3V(+5V TTLとの接続可能)

デットタイム  $0 \sim 2 \, \text{mS} \, ($ 分解能  $^{1}/_{24\,\text{MHz}} )$

2.1.4. パルスジェネレータ(出力)

1) チャンネル数 4チャンネル

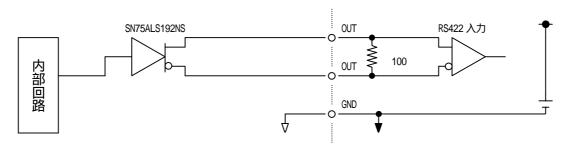

2 ) 出力仕様 RS422レベル + 5 V (SN75ALS192NS)

90°位相差パルス(A,B,Z)相当

3) 出力周波数 0.01Hz~6MHz

4) Z相出力 2~50,000,000パルスに1パルス

5) 割り込み信号 なし

2.1.5. カウンタ(入力)

1) チャンネル数 32bit アップ・ダウン×4チャンネル

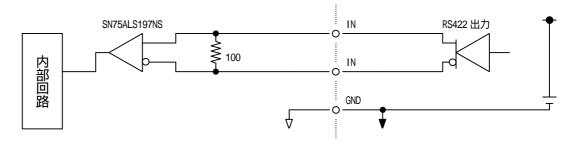

2 ) 入力仕様 RS422レベル + 5 V (SN75ALS197NS)

90°位相差パルス(A,B,Z)

3) 最高入力周波数 5MHz

4) カウンタモード 1,2,4 逓倍切り替え可能 ソフトウェアにより選択可

5) カウンタ長 32bit

6) カウンタプリセット ソフトウェアによるカウンタプリセットが可能

7) カウンタリセット Z相によるカウンタリセットが可能

8 ) リセット許可入力 フォトカプラ絶縁 + 5 V ~ + 2 4 V (PC3Q710NIP)

9) 割り込み信号 なし

2.1.6. 割り込み

1) 内部割り込み パラレル入力ポート、キャプチャポートより可能

2) 外部割り込み

点数 1点

入力仕様 LVTTL + 3.3 V ( + 5 V TTL との接続可能)

CN4-8ピンより入力 最小信号幅:200nSec

エッジ選択可能 ソフトウェアにより選択可

3) DSPへの割り込み ADSP324-00A : INT3

ADSP674-00シリーズ: INT7 割り込みベクター設定可 8種

割り込み信号受付の可否 ソフトウェアにより選択可

2.1.7. ウォッチドグタイマー

1) チャンネル数 1チャンネル

2 ) 監視時間 1 µ S ~ 6 0 S ソフトウェアにより設定可

3 ) 外部出力仕様 TTL + 5 V

CN4 - 11ピンへ出力

2.1.8. リセット

1) ボードの初期化

2) 外部入力仕様 LVTTL + 3.3 V (+5 V TTLとの接続可能)

CN4-15ピンより入力

- 2.1.9. RS232Cポート

- 1) ポート数 1ポート

- 2) 接続 DSP操作ターミナル(ADSP-GOTシリーズ)専用

- 2.1.10. ユーザープログラマブルFPGA

- 1) FPGA FPGA2個をユーザーにてプログラム可能

(IC2, IC3。但し、標準の機能が実装できなくなります)

- 2) ゲート数 1個あたり最大200Kゲート(Xilinx社 スパルタン XC2S200)

- 3) コンフィギュレーション

JTAGにてPROM化(Xilinx社 XC18V02)

- 2.1.11. オプションポート

- 1) ポート数 1ポート

- 2) 接続 ドーターボード専用

- 2.1.12. 増設ボード枚数

最大 4枚

2.1.13. 電源

DC+5V、1A 外部供給(ISAバス)

パラレル入出力 (フォトカプラ絶縁) 使用時 DC+5~24V PWM出力 (フォトカプラ絶縁) 使用時 DC5V、0.5A

## 2.2. ラインナップ

パラレル入出力(LVTTL又はフォトカプラ絶縁)、PWM、キャプチャ、パルスジェネレータ、カウンタの各機能を下表のような組み合わせで実装可能です。

| 機能の組み合わせ          | 型式名                  |

|-------------------|----------------------|

| パラレル入出力 / パラレル入出力 | ADSP324-145   1010 - |

| PWM / カウンタ        | ADSP324-145 PWCN     |

| キャプチャ / パルスジェネレータ | ADSP324-145 CPPL     |

| PWM / パラレル入出力     | ADSP324-145 PWIO -   |

| パラレル入出力 / カウンタ    | ADSP324-145 IOCN -   |

表 2-1 ラインナップの一覧

パラレル入出力を選択されたときの - につきましては、

L V T T L 入出力の場合 : なしフォトカプラ絶縁入出力の場合: - P

PWM、パルスジェネレータには32ビットパラレル入力(フォトカプラ絶縁)が1ポート、キャプチャ、カウンタには32ビットパラレル出力(フォトカプラ絶縁)が1ポート付加されています。

## 3.ハードウェア

## 3.1. コネクタ、ディップスイッチの配置

## 3.2. 出荷時の設定

本ボードの出荷時のディップスイッチ等の設定は下記のように設定されています。

【注意】DSW101~DSW104はユーザーにて変更可能ですが、JP1~JP21はユーザーにての変更はしないでください。

## 3.2.1. ボードアドレス、割り込みフラグ

| DSW101     | 12345678 |                          |

|------------|----------|--------------------------|

| O N<br>OFF |          | ボードアドレス: <u>90</u> 1000h |

| DSW102     | 12345678 |                          |

| 0 N<br>OFF |          | ボードアドレス:90 <u>10</u> 00h |

| DSW103     | 12345678 |                          |

| O N<br>OFF |          | ボードアドレス:9010 <u>00</u> h |

| DSW104     | 12345678 |                          |

| O N<br>OFF |          | 割り込みフラグ:設定無し             |

図 3-2 ディップスイッチの出荷時設定

## 3.2.2. ポート0・1

| 1)               | パラレル入出力                  | (LVTTL)実装時                                                          |                                        |                |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|--------------------------|---------------------------------------------------------------------|----------------------------------------|----------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                          |                                                                     |                                        | :ショ            | <b>1</b> – ト                                       | : オープン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| JP1              | 1 3                      | (なし)                                                                | JP3<br>1<br>3                          | 2 4            | 内部 G N C<br>外部 G N C                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| JP2              | 1 3                      | (なし)                                                                | JP4<br>1<br>3                          | 2 4            | 内部GNE<br>外部GNE                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| JP5              | 13                       | (なし)                                                                | JP7 2 1                                | 4<br>3         | 内部GNE<br>外部GNE                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| JP6              | 1 3                      | (なし)                                                                | JP8 2 1                                | 4<br>3         | 内部GNE<br>外部GNE                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | <u> </u>                 | 3-3 ジャンパースイッラ                                                       | チの出荷時設定                                | (1)            | <u>_</u>                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  |                          |                                                                     |                                        |                |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  |                          |                                                                     |                                        |                |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ۵)               | 110 <b>–</b> 1 11 X 1114 | ✓ → · · · · · · · · · · · · · · · · · ·                             | +                                      |                |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2)               | パラレル入出力                  | (フォトカプラ絶縁)実装明                                                       | <del>†</del>                           | ·シ=            | a <b>–</b> F                                       | ・オープン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>2)</b><br>JP1 | パラレル入出力<br>13            | <b>(フォトカプラ絶縁)実装</b> の<br>フォトカプラ入力側回路<br>と内部VCCを接続                   | JP3<br>1<br>3                          | : ショ<br>2<br>4 | ョート<br>フォトカフ<br>と外部G N                             | :オープン<br><sup>プ</sup> ラ出力側回路<br>J D を接続                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                  |                          | フォトカプラ入力側回路                                                         | JP3                                    | 2              | フォトカフ<br>と外部G N                                    | プラ出力側回路<br>N D を接続<br>プラ出力側回路                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| JP1              | 1 3                      | フォトカプラ入力側回路<br>と内部VCCを接続<br>フォトカプラ入力側回路                             | JP3<br>1<br>3<br>JP4                   | 2 4            | フォトカラ<br>と外部 G N<br>フォトカラ<br>と外部 G N               | プラ出力側回路<br>NDを接続<br>プラ出力側回路<br>NDを接続<br>プラ出力側回路                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| JP1              | 1 3<br>1 3<br>1 3<br>1 3 | フォトカプラ入力側回路<br>と内部VCCを接続<br>フォトカプラ入力側回路<br>と内部VCCを接続<br>フォトカプラ入力側回路 | JP3  1 3  JP4  1 3  JP7  2 1  JP8  2 1 | ] 2 4          | フと フと フと フと フト | プラ出力側回路<br>NDを接続<br>プラ出力側回路<br>NDを接続<br>プラと出力側回路<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>プランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アランカー<br>アカー<br>アの<br>アランカー<br>アランカー<br>アランカー<br>アカー<br>アカー<br>アカー<br>アカー<br>アカー<br>アカー<br>アカー<br>アカー<br>アカー<br>ア |

| 3)  | PWM  | 実装時   |                          |     |          |     |                          |                |

|-----|------|-------|--------------------------|-----|----------|-----|--------------------------|----------------|

| JP1 |      |       |                          | JP3 |          | :ショ | ı <b>–</b> ト             | : オープン         |

| JFI | 1    | 3     | フォトカプラ出力側回路<br>と外部VCCを接続 | Jrs | 1 3      | 2 4 | フォトカプラ<br>と外部GNI         | ラ出力側回路<br>Dを接続 |

| JP2 | 1    | 3     | (なし)                     | JP4 | 1 3      | 2 4 | 内部 G N D a<br>外部 G N D a |                |

| JP5 | 1    | 3     | フォトカプラ入力側回路<br>と外部VCCを接続 | JP7 | 2 1      | 4   | フォトカプ:<br>と内部GNI         | ラ出力側回路<br>Dを接続 |

| JP6 | 1    | 3     | フォトカプラ入力側回路<br>と外部VCCを接続 | JP8 | 2 1      | 4 3 | フォトカプ:<br>と内部GNI         | ラ出力側回路<br>Dを接続 |

|     |      | 図     | 3 - 5 ジャンパースイッチ          | チの出 | <u> </u> | (3) | _                        |                |

|     |      |       |                          |     |          |     |                          |                |

| 4)  | キャプチ | チャー実装 | 舑                        |     |          |     |                          |                |

| ,   |      |       | •                        |     |          | :ショ | ı <b>–</b> ト             | : オープン         |

| JP1 | 1    | 3     | フォトカプラ入力側回路<br>と内部VCCを接続 | JP3 | 1 3      | 2 4 | フォトカプ:<br>と外部GNI         | ラ出力側回路<br>Dを接続 |

| JP2 | 1    | 3     | フォトカプラ入力側回路<br>と内部VCCを接続 | JP4 | 1 3      | 2 4 | フォトカプラ<br>と外部GNI         | ラ出力側回路<br>Dを接続 |

| JP5 | 1    | 3     | (なし)                     | JP7 | 2 1      | 4 3 | 内部 G N D a<br>外部 G N D a |                |

| JP6 | 1    | 3     | (なし)                     | JP8 | 2 1      | 4 3 | (なし)                     |                |

図 3-6 ジャンパースイッチの出荷時設定(4)

## 3.2.3. ポート2・3

| 5) . | パラレル入出 | l力(LVTTL)実装時     |            |     |          |         |

|------|--------|------------------|------------|-----|----------|---------|

|      |        |                  |            | : シ | ョート      | : オープン  |

| JP10 |        |                  | JP11       |     |          |         |

|      | 1 2    | 内部GNDと           | 1          | 2   | 内部GND    | ع(      |

| ;    | 3 4    | 外部GNDを接続         | 3          | 4   | 外部GND    | )を接続    |

| JP12 |        |                  | JP13       |     |          |         |

| :    | 2 4    | 内部GNDと           | 2          | 4   | 内部GND    | ع(      |

|      | 1 3    | 外部GNDを接続         | 1          | 3   | 外部GNC    | )を接続    |

|      |        | 図 3-7 ジャンパースイッ   | チの出荷時設     | 定(5 | )_       |         |

|      |        |                  |            |     |          |         |

| ->   |        |                  | <b>-</b> - |     |          |         |

| 6) . | バラレル人は | 出力 (フォトカプラ絶縁) 実装 | 時          |     |          |         |

|      |        |                  |            | :シ  | ョート      | : オープン  |

| JP10 |        | _                | JP11       |     |          | _       |

|      | 1 2    | フォトカプラ出力側回路      | 1          | 2   |          | プラ出力側回路 |

| ;    | 3 4    | と外部GNDを接続        | 3          | 4   | と外部GN    | ⅡDを接続   |

| JP12 |        |                  | JP13       |     |          |         |

| 2    | 2 4    | (なし)             | 2          | 4   | (なし)     |         |

| •    | 1 3    |                  | 1          | 3   |          |         |

|      |        | 図 3-8 ジャンパースイッ   | チの出荷時設     | 定(6 | <u>)</u> |         |

| コート                                                                                                                                                                                                                                                                                                                                     | 7)  | バルスジェネレ      | ノータ 実装時             |         |      |            |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|---------------------|---------|------|------------|--------|

| 1 2 内部GNDと 1 2 (なし) 3 4 外部GNDを接続 3 4 (なし) 4 外部GNDを接続 3 4 (なし) 3 1 3 3 2 3 - 9 ジャンパースイッチの出荷時設定(7) 8) カウンタ 実装時 :ショート :オープン JP10 JP11 1 2 フォトカプラ出力側回路 1 2 フォトカプラ出力側回路 3 4 と外部GNDを接続 3 4 と外部GNDを接続 3 JP12 JP13 2 4 内部GNDと 2 4 (なし)                                                                                                          |     |              |                     |         | :ショ  | ョート        | : オープン |

| 3 4 外部GNDを接続 3 4  JP12 JP13 2 4 (なし) 2 4 (なし) 3 1 3 3 3 3 3 4 3 4 3 4 3 4 3 4 4 4 4 4                                                                                                                                                                                                                                                   | JP1 | 0            |                     | JP11    |      |            |        |

| JP12       JP13         2       4 (なし)       2 4 (なし)         3       1 3         図 3-9 ジャンパースイッチの出荷時設定(7)         8) カウンタ 実装時       : ショート : オープン         JP10       JP11         1 2 フォトカプラ出力側回路       1 2 フォトカプラ出力側回路         3 4 と外部GNDを接続       3 4 と外部GNDを接続         JP12       JP13         2 4 内部GNDと       2 4 (なし)            |     | 1 2          | 内部GNDと              | 1       | 2    | (なし)       |        |

| 2       4 (なし)       2       4 (なし)         3       図 3-9 ジャンパースイッチの出荷時設定(7)         8) カウンタ 実装時       : ショート : オープン         JP10       JP11         1       2       フォトカプラ出力側回路       1       2       フォトカプラ出力側回路         3       4       と外部GNDを接続       3       4       と外部GNDを接続         JP12       JP13       2       4       (なし) |     | 3 4          | 外部GNDを接続            | 3       | 4    |            |        |

| 2       4 (なし)       2       4 (なし)         3       図 3-9 ジャンパースイッチの出荷時設定(7)         8) カウンタ 実装時       : ショート : オープン         JP10       JP11         1       2       フォトカプラ出力側回路       1       2       フォトカプラ出力側回路         3       4       と外部GNDを接続       3       4       と外部GNDを接続         JP12       JP13       2       4       (なし) | ID4 | 0            |                     | ID40    |      |            |        |

| 1 3 1 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3                                                                                                                                                                                                                                                                                                 | JP1 |              |                     |         | ٦.   |            |        |

| 図 3-9 ジャンパースイッチの出荷時設定(7)  8) カウンタ 実装時                                                                                                                                                                                                                                                                                                   |     |              | (なし)                |         |      | (なし)       |        |

| 8) カウンタ 実装時<br>: ショート : オープン JP10 JP11 1 2 フォトカプラ出力側回路 1 2 フォトカプラ出力側回路 3 4 と外部GNDを接続 3 4 と外部GNDを接続  JP12 JP13 2 4 内部GNDと 2 4 (なし)                                                                                                                                                                                                       |     | 1 3          |                     | 1       | 3    |            |        |

| 8) カウンタ 実装時<br>: ショート : オープン JP10 JP11 1 2 フォトカプラ出力側回路 1 2 フォトカプラ出力側回路 3 4 と外部GNDを接続 3 4 と外部GNDを接続  JP12 JP13 2 4 内部GNDと 2 4 (なし)                                                                                                                                                                                                       |     |              | 図 3-9 ジャンパースイッ      | チの出荷時設定 | Ē(7) | )          |        |

| JP10       JP11         1       2       フォトカプラ出力側回路       1       2       フォトカプラ出力側回路         3       4       と外部GNDを接続       3       4       と外部GNDを接続         JP12       JP13         2       4       内部GNDと       2       4       (なし)                                                                                               |     |              |                     |         |      |            |        |

| JP10       JP11         1       2       フォトカプラ出力側回路       1       2       フォトカプラ出力側回路         3       4       と外部GNDを接続       3       4       と外部GNDを接続         JP12       JP13         2       4       内部GNDと       2       4       (なし)                                                                                               |     |              |                     |         |      |            |        |

| JP10       JP11         1       2       フォトカプラ出力側回路       1       2       フォトカプラ出力側回路         3       4       と外部GNDを接続       3       4       と外部GNDを接続         JP12       JP13         2       4       内部GNDと       2       4       (なし)                                                                                               | 8)  | カウンタ 宝装      | <b>崇時</b>           |         |      |            |        |

| JP10       JP11         1       2       フォトカプラ出力側回路       1       2       フォトカプラ出力側回路         3       4       と外部GNDを接続       3       4       と外部GNDを接続         JP12       JP13         2       4       内部GNDと       2       4       (なし)                                                                                               | Ο,  | 70 7 7 7 7 7 | v                   |         | : ショ | <b>=</b> - | : オープン |

| 3 4 と外部GNDを接続 3 4 と外部GNDを接続  JP12 JP13 4 内部GNDと 2 4 (なし)                                                                                                                                                                                                                                                                                | JP1 | 0            |                     | JP11    |      |            |        |

| 3 4 と外部GNDを接続 3 4 と外部GNDを接続  JP12 JP13 4 内部GNDと 2 4 (なし)                                                                                                                                                                                                                                                                                |     | 1 2          | フォトカプラ出力側回路         | 1       | 2    | フォトカプラ     | ラ出力側回路 |

| JP12 JP13 2 4 内部GNDと 2 4 (なし)                                                                                                                                                                                                                                                                                                           |     | 3 4          |                     | 3       | 4    |            |        |

| 2 4 内部GNDと 2 4 (なし)                                                                                                                                                                                                                                                                                                                     |     |              |                     |         | _    |            |        |

|                                                                                                                                                                                                                                                                                                                                         | JP1 | 2            |                     | JP13    |      |            |        |

|                                                                                                                                                                                                                                                                                                                                         |     | 2 4          | 内部GNDと              | 2       | 4    | (なし)       |        |

|                                                                                                                                                                                                                                                                                                                                         |     | 1 3          | 外部GNDを接続            | 1       | 3    | -          |        |

| 図 3-10 ジャンパースイッチの出荷時設定(8)                                                                                                                                                                                                                                                                                                               |     |              | │<br>│3-10 ジャンパースイッ | ノチの出荷時設 | 定(8  | )          |        |

#### コンフィギュレーションモード 3.2.4. :ショート : オープン IC2のコンフィギュレーションモード選択 JP9 3 18 2 17 PROM(IC5)からコンフィギュレーション 1 16 図 3-11 ジャンパースイッチの出荷時設定(9) 3.2.5. 基準クロック : ショート : オープン IC1(FPGA) 基準クロック選択 JP14 JP17 3 1 3 6 分周設定 12MHz 2 24MHzクロック 1 IC2(FPGA) 基準クロック選択 JP15 JP18 3 3 6 2 24MHzクロック 分周設定 1 2 M H z IC3(FPGA) 基準クロック選択 JP16 JP19 3 3 6 2 4 2 4 M H z クロック 分周設定 12MHz 図 3-12 ジャンパースイッチの出荷時設定(10) 3.2.6. IC電源 : オープン :ショート ライン・ドライバ ICの電源選択 JP20 3 2 1 + 5 V ライン・レシーバ ICの電源選択 JP21 1 2 3 + 5 V

## 3.3. ポードの設置方法

- 1)本ボードを拡張スロットに装着します。

- 2) DSPボードと、本ボードのCN11を拡張バスケーブルで接続します。

| ADSP324-145 | DSPボード            |

|-------------|-------------------|

| C N 1 1     | ADSP324-00A:CN11  |

| CIVII       | ADSP674-00 : CN12 |

表 3-1 DSPボードの接続コネクタ

| 拡張バスケーブル | ADSP324-15 | オプション |

|----------|------------|-------|

|----------|------------|-------|

表 3-2 拡張バスケーブル

パラレル入出力、PMW,キャプチャ、パルスジェネレータ、カウンタは下記コネクタに接続します。

| 機能              | ADSP324-145 |

|-----------------|-------------|

| パラレル入出力(ポート0,1) | C N 1 2     |

| パラレル入出力(ポート2,3) | C N 1 3     |

| PMW             | C N 1 2     |

| キャプチャ           | C N 1 2     |

| パルスジェネレータ       | C N 1 3     |

| カウンタ            | C N 1 3     |

表 3-3 機能別の接続コネクタ

## 3.4. 入出力信号の接続方法

## 3.4.1. LVTTL出力

図 3-14 LVTTL出力回路

## 3.4.2. LVTTL入力

図 3-15 LVTTL入力回路

## 3.4.3. フォトカプラ絶縁出力

図 3-16 フォトカプラ絶縁出力回路

## 3.4.4. フォトカプラ絶縁入力

図 3-17 フォトカプラ絶縁入力回路

## 3.4.5. PWM出力 (フォトカプラ絶縁出力)

図 3-18 PWM出力回路

## 3.4.6. キャプチャ入力(LVTTL入力)

図 3-19 キャプチャ入力回路

## 3.4.7. パルスジェネレータ出力(ライン・ドライバ出力)

図 3-20 パルスジェネレータ出力回路

## 3.4.8. カウンタ入力(ライン・レシーバー入力)

図 3-21 カウンタ入力回路

## 4. 機能説明

#### 4.1. 共通

#### 4.1.1. ウォッチドグタイマ

DSPボードのプログラムが正常に動作しているか否かをチェックし、異常動作(暴走など)を検出した場合、異常の発生を外部へ知らせることができます。異常発生時は、CN4-11ピンが【Hi】(+5Vレベル)になります。

正常時は【Lo】(GNDレベル)になっています(CN4-16ピンがGNDです)。 設定等の詳細は「6.2.2 ウォッチドグタイマ コントロール・レジスタの設定」「6.2.3 ウ ォッチドグタイマ カウントリセット・レジスタ」を参照してください。

#### 4.1.2. リセット

DSPボードなどが異常動作(暴走など)となり、本ボードの制御が不能になったときなど、外部よりリセット信号を入力することで本ボードを初期化状態にすることができます。本ボードへリセット入力を行うときは、CN4-15ピンとCN4-16ピンを短絡(CN4-15ピンを【Lo】(GNDレベル)にする)してください。

#### 4.2. パラレル入出力

#### 4.2.1. 32bitモードと16bitモード

本ボードのパラレル入出力回路は、32bitモードと16bitモードがあります。

#### 1) 32bitモードの出力

32bit用レジスタに書き込まれた <math>32bitデータが、出力ポートの <math>32bitへそのまま出力されます。

#### 2) 16bitモードの出力

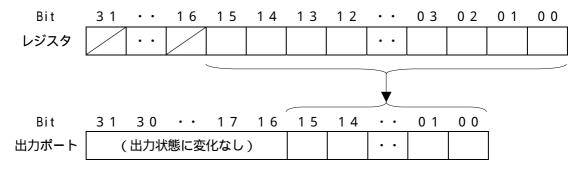

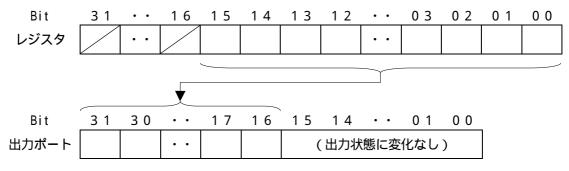

上位16bitと下位bitに分けられます。

#### 下位16bit出力

下位 1 6 b i t 用レジスタに書き込まれた 3 2 b i t データの下位 1 6 b i t のデータが、出力ポートの下位 1 6 b i t へ出力されます。

図 4-1 出力ポート下位16bit

#### 上位16bit出力

上位 16bitmレジスタに書き込まれた 32bitデータの下位 16bitのデータが、出力ポートの上位 16bitへ出力されます。

図 4-2 出力ポート上位16bit

## 3) 32bitモードの入力

入力ポートからの32bitデータが、32bit用レジスタの32bitへそのまま読み込まれます。

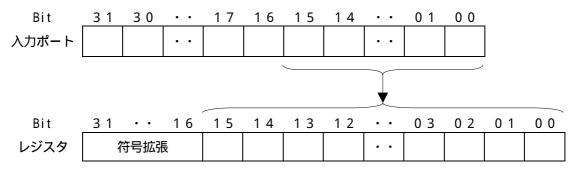

#### 4) 16bitモードの入力

上位16bitと下位bitに分けられます。

#### 下位16bit入力

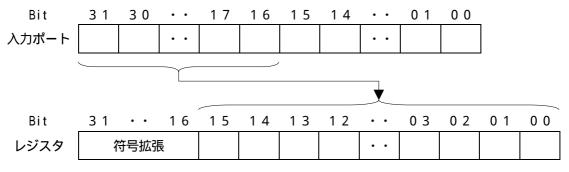

入力ポートからの32bitデータの下位16bitが、下位16bit用レジスタの下位16bitへ読み込まれ、メモリの上位16bitは符号拡張されます。

図 4-3 入力ポート下位16bit

#### 上位16bit入力

入力ポートからの32bitデータの上位16bitが、上位16bit用レジスタの下位16bitへ読み込まれ、メモリの上位16bitは符号拡張されます。

図 4-4 入力ポート上位16bit

符号拡張: bit15が【0】ならばbit16からbit31はすべて【0】 bit15が【1】ならばbit16からbit31はすべて【1】となる。

## 4.2.2. ハンドリング方式

本ボードのパラレル入出力回路は、32bitデータラインとは別に入出力制御用信号があり、3つのハンドリング方式が用意されています。

以下に各ハンドリングのタイムチャートを負論理極性にて記します。

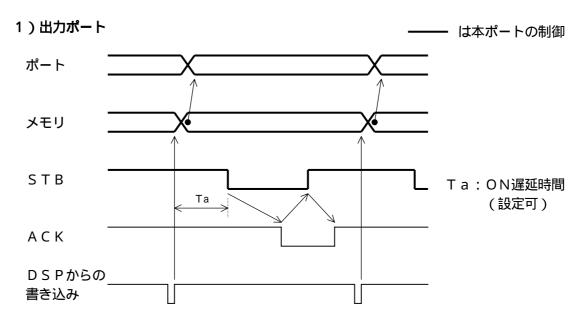

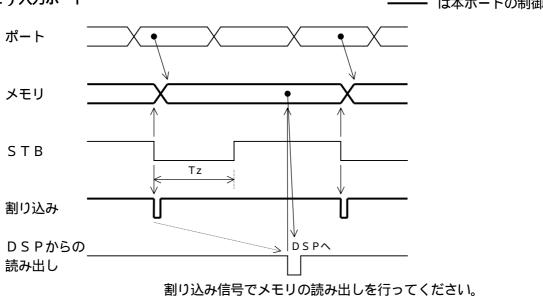

## 1) STB/ACK方式のタイムチャート

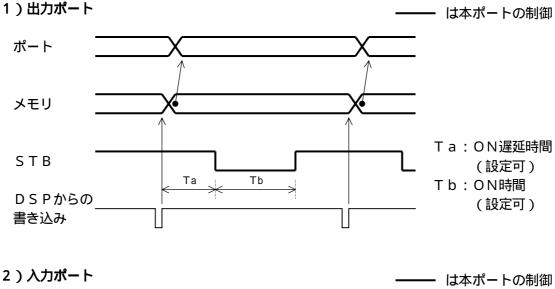

## 2) ライトストロープ方式のタイムチャート

Tz:LVTTL入出力のときは200nSec以上 フォトカプラ絶縁入出力のときは100µSec以上

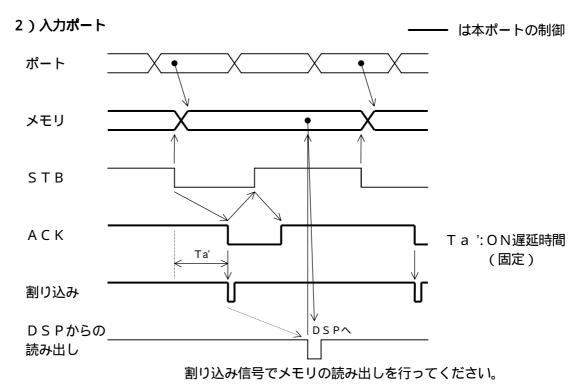

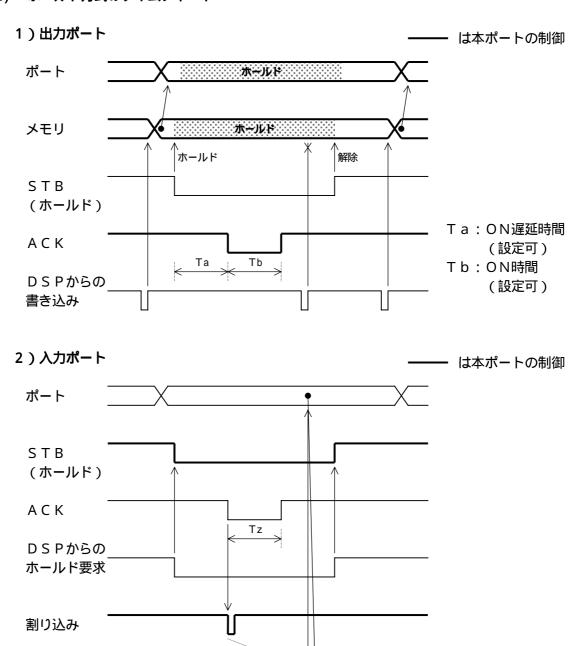

## 3) ホールド方式のタイムチャート

割り込み信号でメモリの読み出しを行ってください。

DSP

DSP

Tz:LVTTL入出力のときは200nSec以上 フォトカプラ絶縁入出力のときは100µSec以上

DSPからの 読み出し

## 4.3. PWM

#### 4.3.1. 3相モードと単相モード

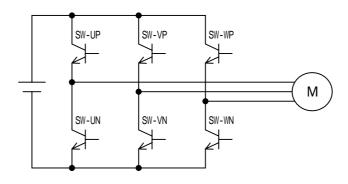

本ボードのPWM出力回路は、3相モードと単相モードがあります。

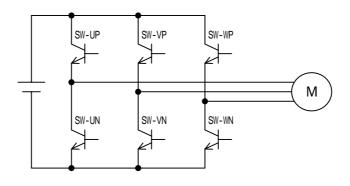

## 1) 3相モードの出力

下図のような回路構成で3相PWM出力を行うことができます。 出力インターフェイスはフォトカプラ絶縁 + 5 Vです。

図 4-5 3相PWM出力の回路構成

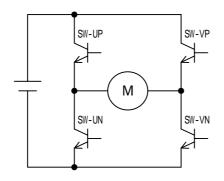

## 2) 単相モードの出力

下図のような回路構成で単相 P W M ( H ブリッジ回路 ) 出力を行うことができます。 出力インターフェイスはフォトカプラ絶縁 + 5 V です。

図 4-6 単相 PWM出力の回路構成

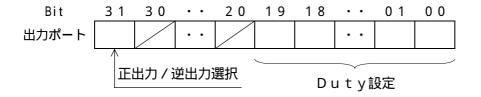

## 4.3.2. 出力波形

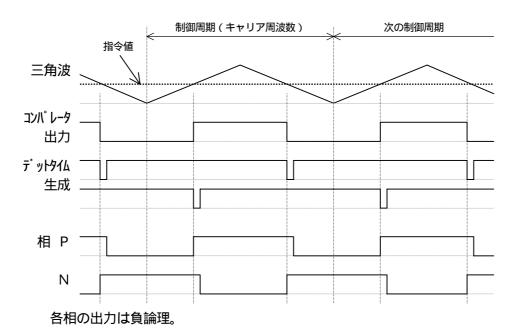

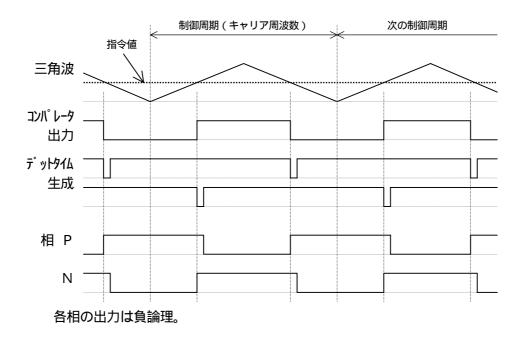

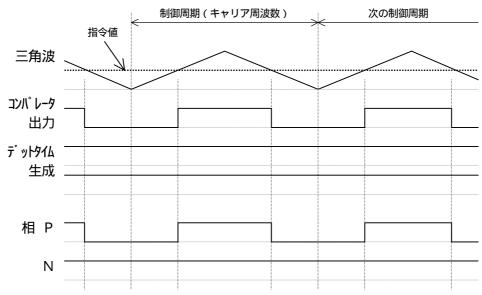

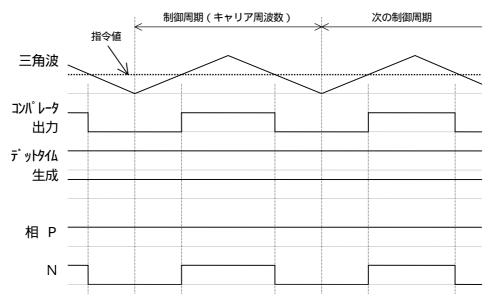

本ボードのPWM出力波形は フルブリッジの正出力、フルブリッジの逆出力 ハーフブリッジの正出力、ハーフブリッジの逆出力 の4通りの出力が可能です。それぞれの出力波形は以下のとおりです。

## 1) フルブリッジの正出力

図 4-7 PWM出力波形 フルブリッジの正出力

## 2) フルブリッジの逆出力

図 4-8 PWM出力波形 フルブリッジの逆出力

## 3) ハーフブリッジの正出力

各相の出力は負論理。

デットタイムは、逆出力に切り替えたときには生成されます。

図 4-9 PWM出力波形 ハーフブリッジの正出力

## 4) ハーフブリッジの逆出力

各相の出力は負論理。

デットタイムは、正出力に切り替えたときには生成されます。

<u>図 4-10 PWM出力波形 ハーフブリッジの逆出力</u>

#### 4.3.3. 同期パルス出力

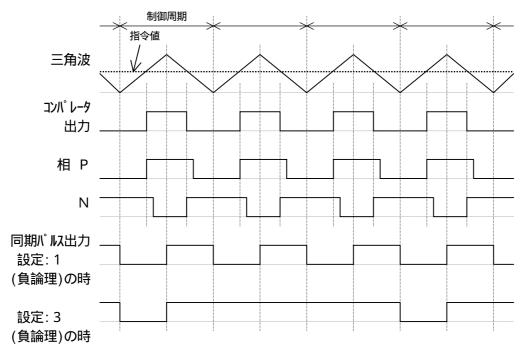

本ボードのPWM波形生成回路では、制御周期(キャリア周波数)に同期したパルス出力が可能です。このパルス信号は、A/D変換開始のトリガに使用するなどPWM制御周期に同期した制御に利用できます。この同期パルス出力はPWM制御周期毎(1周期に1出力)から数周期毎(2~255周期に1出力)の出力設定が可能です。(キャリア周波数設定と同期パルス出力設定を行えば、出力許可と関係なく同期パルスが出力されます)

パルス出力幅はPWM制御周期の1/2幅で出力され、負論理・正論理の出力切り替えが可能です。

図 4-11 同期パルス出力波形

#### 4.3.4. 設定データの反映タイミング

本ボードのPWM波形生成回路では、設定されたキャリア周波数データとDutyデータを反映するタイミングを周期に同期させるか、書き込み時に反映するかを選択できます。

### 1) 周期に同期して反映

「図 4-7 PWM出力波形 フルブリッジの正出力」の制御周期の途中でデータが書き込まれても波形生成回路には反映されず(出力波形には影響はなく)次の制御周期へ切り替わったときにデータが反映されますので安定した出力が得られます。但し、最大1周期分の制御遅れが発生します。

### 2) 書き込み時に反映

データの書き込みがおこなわれた時点ですぐ波形生成回路に反映されます。データの書き込みが行われたときの制御周期での出力は意図しない波形となる場合がありますが、早く制御を切り替えることができます。

#### 4.4. キャプチャ

#### 4.4.1. 3相モードと単相モード

本ボードのキャプチャの波形入力回路は、3相PWMモードと単相PWMモードがあります。

## 1) 3相モードの入力

下図のような回路構成している3相PWM出力の波形をキャプチャすることができます。 本ボードの入力ピンへは、それぞれ図中トランジスタを駆動する信号を接続してください。 但し、入力インターフェイスはLVTTLです。

図 4-12 3相PWMのキャプチャ可能回路構成

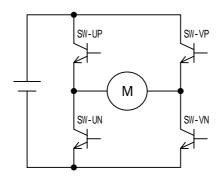

## 2) 単相モードの入力

下図のような回路構成している単相PWM(Hブリッジ回路)出力の波形をキャプチャすることができます。

本ボードの入力ピンへは、それぞれ図中トランジスタを駆動する信号を接続してください。 但し、入力インターフェイスはLVTTLです。

図 4-13 <u>単相 P W M の キャプチャ可能回路構成</u>

#### 4.4.2. 計測データ

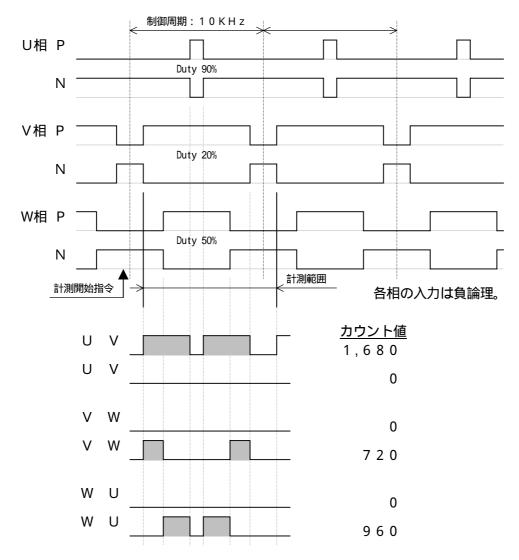

本ボードのキャプチャにて計測したときの計測データの考え方は下記のとおりです。

図 4-14 キャプチャしたPWM波形

「図 4-14 キャプチャしたPWM波形」のPWM波形をキャプチャした場合、各レジスタの

値は、制御周期 : 2,400

UV相 ON時間

: 1,680

VU相 ON時間

: 0

VW相 ON時間

: 720

WU相 ON時間

: 960

となります。この値は各波形の組み合わせ入力を基準クロック 2 4 M H z ( 4 1 . 6 6・n S e c ) でカウントした値です。

制御周期データは、入力された制御波形の1周期の時間を基準クロックでカウントした値です。 (入力波形の内、いずれか1つの入力波形を計測します。)

各ON時間データは、入力された制御波形から各相間がONした時間を基準クロックでカウントした値です。例えば、UV相 ON時間はU相が+でV相が-のとき(電流方向がU相 V相)のカウント値で、VU相 ON時間はV相が+でU相が-のとき(電流方向がV相 U相)のカウント値です。

#### 4.5. パルスジェネレータ

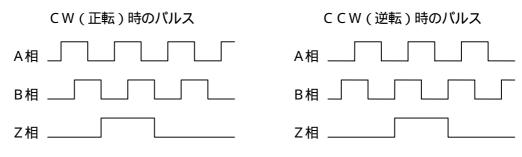

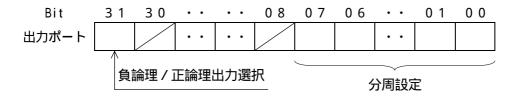

#### 4.5.1. CW出力とCCW出力

本ボードのパルスジェネレータのパルス生成回路は、CW(正転)のときにA相がB相に対して進み位相のパルスを生成します。

図 4-15 CW・CCWパルスの生成

## 4.5.2. 出力波形

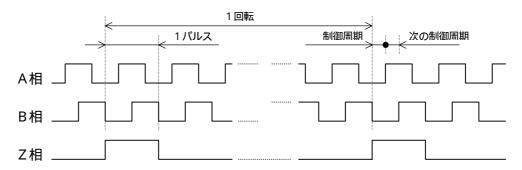

本ボードのパルスジェネレータの出力波形は下図のとおりです。

図 4-16 パルスジェネレータの出力波形

## 4.5.3. 周期データの反映タイミング

本ボードのパルスジェネレータのパルス生成回路では、設定されたパルス周期データを反映するタイミングを周期に同期させるか、書き込み時に反映するかを選択できます。

#### 1) 周期に同期して反映

「図 4-16 パルスジェネレータの出力波形」の制御周期の途中でデータが書き込まれても パルス生成回路には反映されず(出力波形には影響はなく)次の制御周期へ切り替わったとき にデータが反映されますので安定した出力が得られます。但し、最大1周期分の制御遅れが発 生します。

## 2) 書き込み時に反映

データの書き込みがおこなわれた時点ですぐ波形生成回路に反映されます。データの書き込みが行われたときの制御周期での出力は意図しない波形となる場合がありますが、早く制御を切り替えることができます。

## 4.5.4. 回転方向データの反映タイミング

本ボードのパルスジェネレータのパルス生成回路では、回転方向データは書き込み時に反映されます。

# 4.6. カウンタ

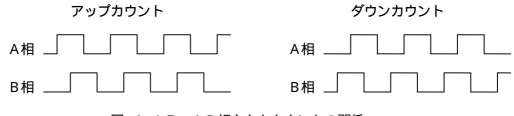

# 4.6.1. カウンタのアップ・ダウン

本ボードのカウンタの値は、A相がB相に対して進み位相のときにアップカウントします。

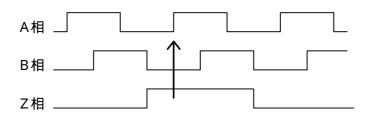

図 4-17 AB相入力とカウントの関係

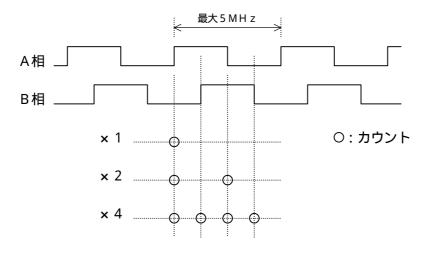

# 4.6.2. カウンタの逓倍

本ボードのカウンタの逓倍は、下記のようになっています。

図 4-18 カウンタの逓倍

# 4.6.3. カウンタリセット

本ボードのカウンタ回路は外部よりカウンタ毎にリセットがかけることができるようになっています。リセットさせるには、カウンタリセット・レジスタに【1】を設定し、絶縁入力指定ビットが【1】(絶縁入力端子をGNDレベルにする)で、Z相が【Hi】、B相が【Lo】のときのA相の立ち上がり又は立ち下がりでゼロリセットされます。

| チャンネル   | カウンタリセット | 絶縁入力      | Z相   | B相   | A相      |

|---------|----------|-----------|------|------|---------|

|         | 許可レジスタ   | 指定ビット     |      |      |         |

| チャンネル3  | bit4     | CN13-74ピン | 【Hi】 | [Lo] | 立ち上がり又は |

|         | 【1】      | 【1】       |      |      | 立ち下がり   |

| チャンネル2  | bit3     | CN13-73ピン | 【Hi】 | [Lo] | 立ち上がり又は |

|         | 【1】      | 【1】       |      |      | 立ち下がり   |

| チャンネル 1 | bit2     | CN13-72ピン | 【Hi】 | [Lo] | 立ち上がり又は |

|         | 【1】      | 【1】       |      |      | 立ち下がり   |

| チャンネル 0 | bit1     | CN13-71ピン | 【Hi】 | [Lo] | 立ち上がり又は |

|         | [1]      | [1]       |      |      | 立ち下がり   |

表 4-1 カウンタリセット条件

図 4-19 ABZ相のカウンタリセット条件

# 5.初期設定

本ボードで初期設定が必要なものはディップスイッチ【DSW101】~【DSW104】とメモリマップされた各レジスタがあります。ディップスイッチの設定は大きく分けて2つの部分から構成されています。

- 1.ボードアドレスの設定

- 2.割り込みフラグの設定

#### また、レジスタには

- 1. ウォッチドグタイマ コントロール

- 2.割り込みコントロール

- 3 . 各機能別の設定

などがあり、機能内容の選択のために初期設定を行います。

【注意】ディップスイッチの論理は下記のように定義されています。

| DSW***     | 12345678 |                                                                       |

|------------|----------|-----------------------------------------------------------------------|

| O N<br>OFF |          | D S W * * * の 1 ~ 4 の設定が " O N "、<br>5 ~ 8 の設定が " O F F " の状態を示しています。 |

| DSW | 0 N | OFF |

|-----|-----|-----|

| 論 理 | 0   | 1   |

図 5-1 ディップスイッチの論理表

#### 5.1. 共通

#### 5.1.1. ボードアドレスの設定

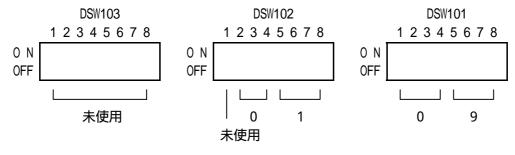

本ボードはアドレスラインのA00~A08をデコードし、200h(512)ワードの領域を使用します。そして【DSW101】~【DSW102】を使用してA09~A23のアドレスを設定し90000h~90FFFFhの64Kワードの領域内に割り付けます。

下記に【DSW101】~【DSW103】のアドレス信号割り付けと設定例を示します。 また、拡張ボードは1台のDSPボードに対して4台まで接続することができますので、アドレスが重ならないように設定してください。

| D S | W 1 0 1 |

|-----|---------|

| 番号  | 信号名     |

| 8   | A 2 3   |

| 7   | A 2 2   |

| 6   | A 2 1   |

| 5   | A 2 0   |

| 4   | A 1 9   |

| 3   | A 1 8   |

| 2   | A 1 7   |

| 1   | A 1 6   |

| DSW102 |       |  |  |

|--------|-------|--|--|

| 番号     | 信号名   |  |  |

| 8      | A 1 5 |  |  |

| 7      | A 1 4 |  |  |

| 6      | A 1 3 |  |  |

| 5      | A 1 2 |  |  |

| 4      | A 1 1 |  |  |

| 3      | A 1 0 |  |  |

| 2      | A 0 9 |  |  |

| 1      | 未使用   |  |  |

| DSW103 |     |  |

|--------|-----|--|

| 番号     | 信号名 |  |

| 8      | 未使用 |  |

| 7      | 未使用 |  |

| 6      | 未使用 |  |

| 5      | 未使用 |  |

| 4      | 未使用 |  |

| 3      | 未使用 |  |

| 2      | 未使用 |  |

| 1      | 未使用 |  |

表 5-1 DSW101~DSW103の信号割り付け表

ボードアドレス:901000h

図 5-2 ボードアドレスの設定

【注意】ADSP324-00Aでは上記アドレス通りに割り付けられますが、 ADSP674-00では0300000h~033EFFFFh (0300000h~0303FFFFh)に割り付けられます。 (ADSP674-00 ハードウェアマニュアル「拡張バス」参照)

(例)本ボードのアドレスを901000hに設定した場合、 ADSP674-00のアドレスは03004000hになります。

# 5.1.2. 割り込みフラグ

割り込みフラグはどの周辺ボードが割り込みを発生しているかを識別するためのものです。ボード毎に任意のフラグを【DSW104】を使って設定することができます。DSPボードにはこの割り込みフラグを90FFFFhのD00~D07より読み出すことができます。下記に【DSW104】のデータ信号割り付けと出荷時の設定を示します。

|    | DSW104    |               |  |  |  |  |

|----|-----------|---------------|--|--|--|--|

| 番号 | 信号名       | 9 0 F F F F h |  |  |  |  |

| 8  | 割り込みフラグ8  | D 0 7         |  |  |  |  |

| 7  | 割り込みフラグ 7 | D 0 6         |  |  |  |  |

| 6  | 割り込みフラグ 6 | D 0 5         |  |  |  |  |

| 5  | 割り込みフラグ 5 | D 0 4         |  |  |  |  |

| 4  | 割り込みフラグ4  | D 0 3         |  |  |  |  |

| 3  | 割り込みフラグ3  | D 0 2         |  |  |  |  |

| 2  | 割り込みフラグ 2 | D 0 1         |  |  |  |  |

| 1  | 割り込みフラグ 1 | D 0 0         |  |  |  |  |

表 5-2 DSW104の信号割り付け表

割り込みフラグ:設定なし

DSW104 1 2 3 4 5 6 7 8 0 N 0FF

図 5-3 割り込みフラグの設定

# 5.1.3. 割り込みコントロール・レジスタの設定

割り込みコントロール・レジスタは、割り込みの許可/未許可の選択を行います。電源投入時、このレジスタはイニシャルリセットされ【bit0】~【bit10】はすべて【0】になっています。

【bit2】~【bit9】は、実装される機能により多少異なります。

| 割り込みコントロール レジスタ | 0               | 1            |

|-----------------|-----------------|--------------|

| bit10           | 外部割り込みの未許可      | 外部割り込みの許可    |

| bit9            | ポート3Hの割り込み未許可   | ポート3Hの割り込み許可 |

| bit8            | ポート3Lの割り込み未許可   | ポート3Lの割り込み許可 |

| bit7            | -               | -            |

| bit6            | -               | -            |

| bit5            | ポート 1 Hの割り込み未許可 | ポート1Hの割り込み許可 |

| bit4            | ポート1L/キャプチャ     | ポート1L/キャプチャ  |

|                 | の割り込み未許可        | の割り込み許可      |

| bit3            | -               | -            |

| bit2            | -               | -            |

| bit1            | 全割り込み未許可        | 全割り込み許可      |

| bit0            | 外部割り込みの         | 外部割り込みの      |

|                 | トリガスロープ         | トリガスロープ      |

表 5-3 割り込みコントロール・レジスタ

#### 5.2. パラレル入出力

この機能を使用するときの初期設定する必要のあるレジスタには

- 1.モード、ハンドリング方式選択

- 2. ハンドリング信号の極性(LVTTLのみ)

- 3. ハンドリング信号のON時間

- 4. ハンドリング信号のON遅延時間

などがあり、機能内容の選択のために初期設定を行います。

なお、初期状態では、モード【32bit】 ハンドリング方式【なし】 ハンドリング信号の極性 【負論理】 ハンドリング信号のON時間【0】 ハンドリング信号のON遅延時間【0】となっています。

#### 5.2.1. モード・ハンドリング方式選択・レジスタの設定

モード・ハンドリング方式選択・レジスタは、各ポートのモード【32bit】【16bit】の選択と、各ポートのハンドリング方式の【なし】【STB/ACK】【ライトストローブ】【ホールド】選択を行うことができます。電源投入時、このレジスタはイニシャルリセットされ【bit 0 】~【bit 17】はすべて【0】になっています。

| E-ド レジスタ |           | 0         | 1     |

|----------|-----------|-----------|-------|

| bit17    | 入力ポート 1/3 | 3 2 b i t | 16bit |

| bit16    | 出力ポート 0/2 | 32bit     | 16bit |

表 5-4 モード選択・レジスタ

| ハント・リング 方式 レシ・スタ |       |    | なし | STB  | ライト   | ホールト゛ |

|------------------|-------|----|----|------|-------|-------|

|                  |       |    |    | /ACK | ストローブ |       |

| bit15            | 入力ポート | 上位 | 1  | -    | -     | -     |

| bit14            | 1 / 3 |    | 0  | 0    | 0     | 1     |

| bit13            |       |    | 0  | 0    | 1     | 0     |

| bit12            |       |    | 0  | 1    | 0     | 0     |

| bit11            |       | 下位 | -  | -    | -     | -     |

| bit10            |       |    | 0  | 0    | 0     | 1     |

| bit9             |       |    | 0  | 0    | 1     | 0     |

| bit8             |       |    | 0  | 1    | 0     | 0     |

| bit7             | 出力ポート | 上位 | 1  | -    | -     | -     |

| bit6             | 0 / 2 |    | 0  | 0    | 0     | 1     |

| bit5             |       |    | 0  | 0    | 1     | 0     |

| bit4             |       |    | 0  | 1    | 0     | 0     |

| bit3             |       | 下位 | 1  | -    | -     | -     |

| bit2             |       |    | 0  | 0    | 0     | 1     |

| bit1             |       |    | 0  | 0    | 1     | 0     |

| bit0             |       |    | 0  | 1    | 0     | 0     |

各ポートのモード選択が【32ビット】のときは、上位側の設定が有効になります。

表 5-5 ハンドリング方式・レジスタ

#### 5.2.2. ハンドリング信号の極性・レジスタの設定

ハンドリング信号の極性・レジスタは、各ポートのハンドリング信号の極性【負論理】【正論理】 の選択を行うことができます。電源投入時、このレジスタはイニシャルリセットされ【bit0】 ~【bit7】はすべて【0】になっています。

| ハント゛リンク゛信号の状態<br>レシ゛スタ |       |    |     | 0   | 1   |

|------------------------|-------|----|-----|-----|-----|

| bit7                   | 入力ポート | 上位 | ACK | 負論理 | 正論理 |

| bit6                   |       |    | STB | 負論理 | 正論理 |

| bit5                   |       | 下位 | ACK | 負論理 | 正論理 |

| bit4                   |       |    | STB | 負論理 | 正論理 |

| bit3                   | 出力ポート | 上位 | ACK | 負論理 | 正論理 |

| bit2                   |       |    | STB | 負論理 | 正論理 |

| bit1                   |       | 下位 | ACK | 負論理 | 正論理 |

| bit0                   |       |    | STB | 負論理 | 正論理 |

各ポートのモード選択が【32ビット】のときは、上位側の設定が有効になります。

表 5-6 ハンドリング信号の極性・レジスタ

#### 5.2.3. ハンドリング信号ON時間・レジスタの設定

ハンドリング信号ON時間・レジスタは、各ポートのハンドリング信号ON時間の設定を行うことができます。電源投入時、このレジスタはイニシャルリセットされ【0】になっています。 ハンドリングの詳細につきなしては、「4.2.2 ハンドリング方式」を参照してください。